Pemicu adalah elemen teknologi digital, perangkat bistable yang beralih ke salah satu status dan dapat tetap berada di dalamnya tanpa batas waktu bahkan ketika sinyal eksternal dihilangkan. Itu dibangun dari elemen logis dari tingkat pertama (DAN-BUKAN, ATAU-BUKAN, dll.) Dan milik perangkat logis dari tingkat kedua.

Dalam praktiknya, flip-flop diproduksi dalam bentuk sirkuit mikro dalam paket terpisah atau dimasukkan sebagai elemen dalam sirkuit terintegrasi besar (LSI) atau array logika yang dapat diprogram (PLM).

Isi

Klasifikasi dan jenis sinkronisasi pemicu

Pemicu terbagi menjadi dua kelas besar:

- asinkron;

- sinkron (berjam).

Perbedaan mendasar di antara mereka adalah bahwa untuk kategori perangkat pertama, tingkat sinyal output berubah secara bersamaan dengan perubahan sinyal pada input (input).Untuk pemicu sinkron, perubahan status hanya terjadi jika ada sinyal sinkronisasi (jam, strobo) pada input yang disediakan untuk ini. Untuk ini, output khusus disediakan, dilambangkan dengan huruf C (jam). Menurut jenis gating, elemen sinkron dibagi menjadi dua kelas:

- dinamis;

- statis.

Untuk tipe pertama, tingkat output berubah tergantung pada konfigurasi sinyal input pada saat munculnya bagian depan (tepi depan) atau jatuhnya pulsa clock (tergantung pada jenis pemicu tertentu). Di antara tampilan sinkronisasi front (lereng), sinyal apa pun dapat diterapkan ke input, status pemicu tidak akan berubah. Pada opsi kedua, tanda clocking bukanlah perubahan level, tetapi adanya satu atau nol pada input Clock. Ada juga perangkat pemicu kompleks yang diklasifikasikan berdasarkan:

- jumlah keadaan stabil (3 atau lebih, berbeda dengan 2 untuk elemen utama);

- jumlah level (juga lebih dari 3);

- karakteristik lain.

Elemen kompleks digunakan terbatas pada perangkat tertentu.

Jenis pemicu dan cara kerjanya

Ada beberapa tipe dasar pemicu. Sebelum memahami perbedaannya, properti umum harus diperhatikan: ketika daya diterapkan, output perangkat apa pun diatur ke status arbitrer. Jika ini penting untuk keseluruhan operasi sirkuit, sirkuit preset harus disediakan. Dalam kasus paling sederhana, ini adalah rangkaian RC yang menghasilkan sinyal untuk mengatur keadaan awal.

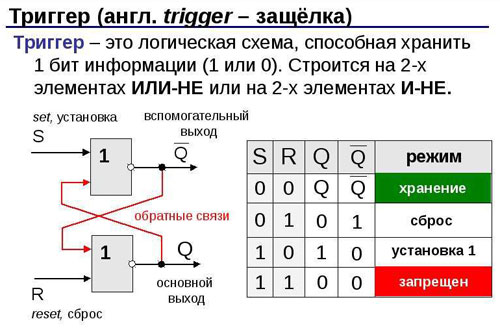

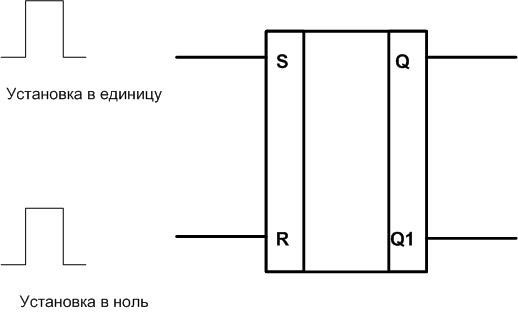

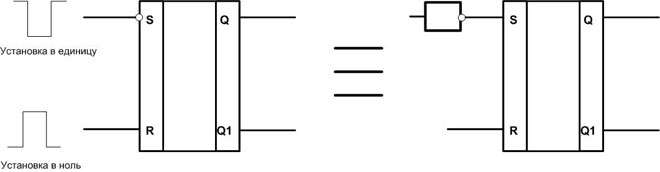

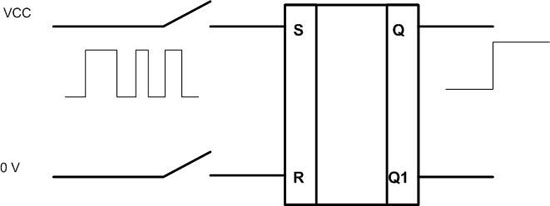

sandal jepit RS

Jenis perangkat bistable asinkron yang paling umum adalah RS flip-flop. Ini mengacu pada flip-flop dengan pengaturan terpisah dari status 0 dan 1.Ada dua masukan untuk ini:

- S - set (instalasi);

- R - setel ulang (reset).

Ada keluaran langsung Q, bisa juga ada keluaran terbalik Q1. Level logika di atasnya selalu kebalikan dari level pada Q - ini berguna saat mendesain sirkuit.

Ketika level positif diterapkan pada input S, output Q akan diatur ke unit logis (jika ada output terbalik, itu akan menuju ke level 0). Setelah itu, pada input pengaturan, sinyal dapat berubah sesuka Anda - ini tidak akan memengaruhi level output. Sampai 1 muncul pada input R. Ini akan mengatur flip-flop ke keadaan 0 (1 pada output terbalik). Sekarang mengubah sinyal pada input reset tidak akan mempengaruhi status elemen selanjutnya.

Penting! Opsi ketika ada unit logis di kedua input dilarang. Pemicu akan disetel ke status arbitrer. Saat merancang skema, situasi ini harus dihindari.

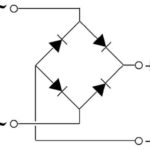

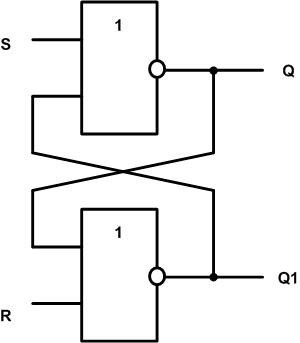

Flip-flop RS dapat dibangun berdasarkan elemen NAND dua input yang banyak digunakan. Metode ini diimplementasikan baik pada sirkuit mikro konvensional maupun di dalam matriks yang dapat diprogram.

Satu atau kedua input dapat dibalik. Ini berarti bahwa pada pin ini, pemicu dikendalikan oleh tampilan bukan level tinggi, tetapi level rendah.

Jika Anda membangun flip-flop RS pada elemen AND-NOT dua input, maka kedua input akan terbalik - dikendalikan oleh suplai nol logis.

Ada versi flip-flop RS yang terjaga keamanannya. Ini memiliki input tambahan C. Switching terjadi ketika dua kondisi terpenuhi:

- kehadiran level tinggi pada input Set atau Reset;

- adanya sinyal clock.

Elemen semacam itu digunakan dalam kasus di mana peralihan harus ditunda, misalnya, pada saat akhir transien.

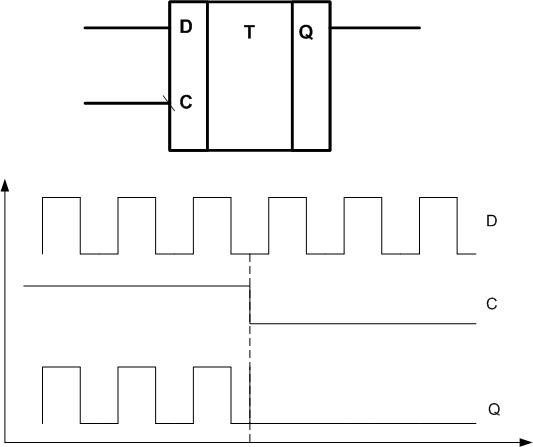

D sandal jepit

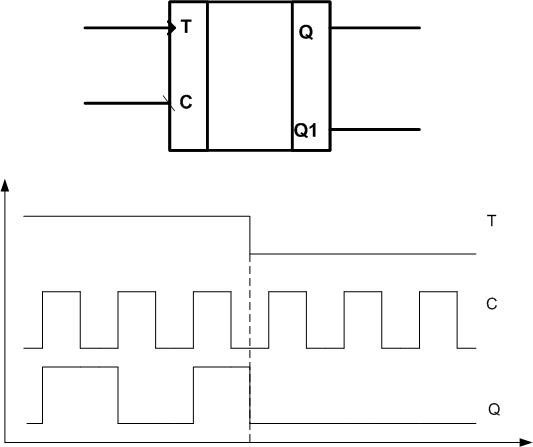

D-trigger ("pemicu transparan", "latch", latch) termasuk dalam kategori perangkat sinkron, di-clock oleh input C. Ada juga input data D (Data). Dalam hal fungsionalitas, perangkat ini termasuk pemicu dengan penerimaan informasi melalui satu input.

Selama yang logis hadir pada input clock, sinyal pada output Q mengulangi sinyal pada input data (mode transparansi). Segera setelah level strobo menjadi 0, level pada output Q akan tetap sama seperti pada saat tepi (latches). Jadi Anda dapat memperbaiki level input pada input kapan saja. Ada juga D-sandal jepit dengan jam di bagian depan. Mereka mengunci sinyal di tepi positif strobo.

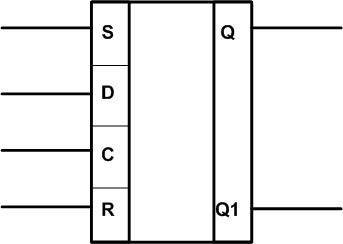

Dalam praktiknya, dua jenis perangkat bistable dapat digabungkan dalam satu sirkuit mikro. Misalnya flip-flop D dan RS. Dalam hal ini, input Set/Reset memiliki prioritas. Jika ada nol logis pada mereka, maka elemen berperilaku seperti D-flip-flop normal. Ketika level tinggi terjadi setidaknya satu input, output diatur ke 0 atau 1, terlepas dari sinyal pada input C dan D.

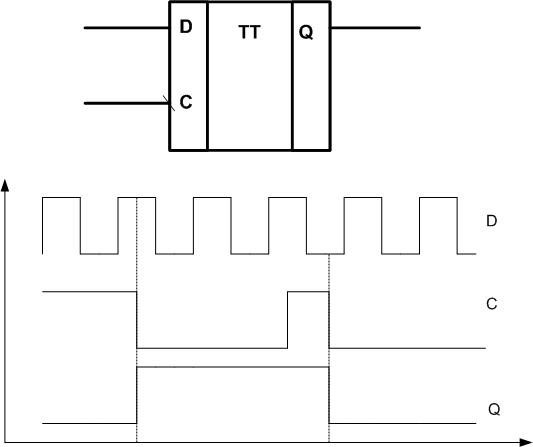

Transparansi flip-flop D tidak selalu merupakan fitur yang berguna. Untuk menghindarinya, elemen ganda digunakan (flip-flop, pemicu "bertepuk"), mereka dilambangkan dengan huruf TT. Pemicu pertama adalah kait biasa yang melewatkan sinyal input ke output. Pemicu kedua berfungsi sebagai elemen memori. Kedua perangkat memiliki clock dengan satu strobo.

sandal jepit

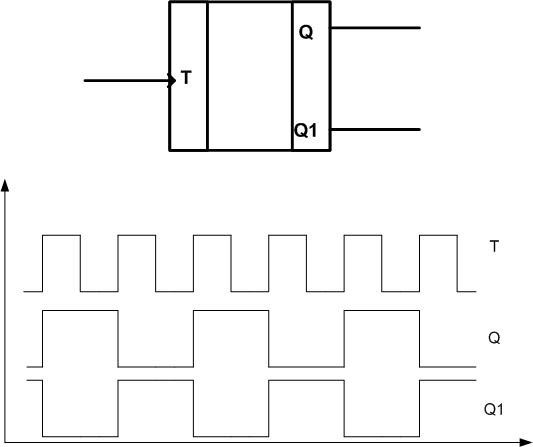

Pemicu T termasuk dalam kelas elemen bistable yang dapat dihitung. Logika kerjanya sederhana - ia mengubah statusnya setiap kali unit logis berikutnya masuk ke inputnya.Jika sinyal pulsa diterapkan ke input, frekuensi output akan dua kali lebih tinggi dari input. Pada output terbalik, sinyal akan keluar fase dengan yang langsung.

Beginilah cara kerja T-flip-flop asinkron. Ada juga opsi sinkron. Ketika sinyal pulsa diterapkan ke input clock dan dengan adanya unit logis pada output T, elemen berperilaku dengan cara yang sama seperti elemen asinkron - ia membagi frekuensi input menjadi dua. Jika pin T berlogika nol, maka output Q disetel rendah, terlepas dari adanya strobo.

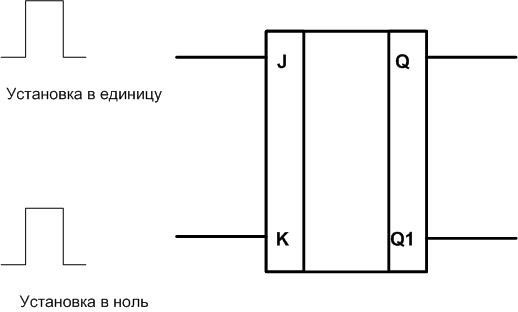

sandal jepit JK

sandal jepit JK

Elemen bistable ini termasuk dalam kategori universal. Itu dapat dikontrol secara terpisah oleh input. Logika flip-flop JK mirip dengan kerja elemen RS. Input J (Job) digunakan untuk mengatur output menjadi satu. Level tinggi pada pin K (Keep) mengatur ulang output ke nol. Perbedaan mendasar dari pemicu RS adalah bahwa kemunculan simultan dari dua input kontrol tidak dilarang. Dalam hal ini, output elemen mengubah statusnya menjadi kebalikannya.

Jika output Job dan Keep terhubung, maka JK-flip-flop berubah menjadi T-flip-flop pencacah asinkron. Ketika gelombang persegi diterapkan pada input gabungan, output akan menjadi setengah frekuensi. Seperti elemen RS, ada versi clock dari flip-flop JK. Dalam praktiknya, elemen jenis ini terutama digunakan.

Penggunaan praktis

Properti pemicu untuk menyimpan informasi yang direkam bahkan ketika sinyal eksternal dihilangkan memungkinkan mereka untuk digunakan sebagai sel memori dengan kapasitas 1 bit.Dari elemen tunggal, Anda dapat membuat matriks untuk menyimpan status biner - menurut prinsip ini, memori akses acak statis (SRAM) dibangun. Fitur memori semacam itu adalah sirkuit sederhana yang tidak memerlukan pengontrol tambahan. Oleh karena itu, SRAM tersebut digunakan dalam pengontrol dan PLA. Tetapi kepadatan perekaman yang rendah mencegah penggunaan matriks seperti itu di PC dan sistem komputasi kuat lainnya.

Penggunaan flip-flop sebagai pembagi frekuensi telah disebutkan di atas. Elemen bistabil dapat dihubungkan dalam rantai dan mendapatkan rasio pembagian yang berbeda. String yang sama dapat digunakan sebagai penghitung pulsa. Untuk melakukan ini, perlu untuk membaca keadaan output dari elemen perantara pada setiap saat - kode biner akan diperoleh sesuai dengan jumlah pulsa yang masuk ke input elemen pertama.

Bergantung pada jenis pemicu yang diterapkan, penghitung dapat sinkron atau asinkron. Konverter serial-ke-paralel dibangun dengan prinsip yang sama, tetapi hanya elemen gerbang yang digunakan di sini. Juga, garis tunda digital dan elemen lain dari teknologi biner dibangun di atas pemicu.

Sandal jepit RS digunakan sebagai penjepit level (penekan pantulan). Jika sakelar mekanis (tombol, sakelar) digunakan sebagai sumber level logika, maka ketika ditekan, efek pantulan akan membentuk banyak sinyal, bukan satu. Flip-flop RS berhasil melawan ini.

Cakupan perangkat bistable sangat luas. Kisaran tugas yang diselesaikan dengan bantuan mereka sangat tergantung pada imajinasi perancang, terutama di bidang solusi non-standar.

Artikel serupa: